## Chapter 10

# Watchdog Timer+

The watchdog timer+ (WDT+) is a 16-bit timer that can be used as a watchdog or as an interval timer. This chapter describes the WDT+ The WDT+ is implemented in all MSP430x2xx devices.

| Topic |                 |              | Page |

|-------|-----------------|--------------|------|

| 10.1  | Watchdog Timer+ | Introduction | 10-2 |

| 10.2  | Watchdog Timer+ | Operation    | 10-4 |

| 10.3  | Watchdog Timer+ | Registers    | 10-7 |

## 10.1 Watchdog Timer+ Introduction

The primary function of the watchdog timer+ (WDT+) module is to perform a controlled system restart after a software problem occurs. If the selected time interval expires, a system reset is generated. If the watchdog function is not needed in an application, the module can be configured as an interval timer and can generate interrupts at selected time intervals.

| Features of the watchdog timer+ module include: |                                                       |  |  |  |  |

|-------------------------------------------------|-------------------------------------------------------|--|--|--|--|

|                                                 | Four software-selectable time intervals               |  |  |  |  |

|                                                 | Watchdog mode                                         |  |  |  |  |

|                                                 | Interval mode                                         |  |  |  |  |

|                                                 | Access to WDT+ control register is password protected |  |  |  |  |

|                                                 | Control of RST/NMI pin function                       |  |  |  |  |

|                                                 | Selectable clock source                               |  |  |  |  |

|                                                 | Can be stopped to conserve power                      |  |  |  |  |

|                                                 | Clock fail-safe feature                               |  |  |  |  |

| The                                             | The WDT+ block diagram is shown in Figure 10–1.       |  |  |  |  |

|                                                 |                                                       |  |  |  |  |

#### Note: Watchdog Timer+ Powers Up Active

After a PUC, the WDT+ module is automatically configured in the watchdog mode with an initial 32768 clock cycle reset interval using the DCOCLK. The user must setup or halt the WDT+ prior to the expiration of the initial reset interval.

WDTCTL MDB **MSB** Q6 3 Q9 WDTQn Int. 2 Flag Q13 Q15 0 16-bit Password Pulse Compare Counter A B Generator 16-bit Clear PUC -CLK (Asyn) EQU Write Enable EQU Low Byte Fail-Safe  $R/\overline{W}$ MCLK-Logic WDTHOLD SMCLK -ACLK -**WDTNMIES** WDTNMI ΕN WDTTMSEL WDTCNTCL WDTSSEL WDTIS1 WDTIS0 LSB MCLK Active Clock Request SMCLK Active Logic

Figure 10-1. Watchdog Timer+ Block Diagram

ACLK Active

## 10.2 Watchdog Timer+ Operation

The WDT+ module can be configured as either a watchdog or interval timer with the WDTCTL register. The WDTCTL register also contains control bits to configure the RST/NMI pin. WDTCTL is a 16-bit, password-protected, read/write register. Any read or write access must use word instructions and write accesses must include the write password 05Ah in the upper byte. Any write to WDTCTL with any value other than 05Ah in the upper byte is a security key violation and triggers a PUC system reset regardless of timer mode. Any read of WDTCTL reads 069h in the upper byte. The WDT+ counter clock should be slower or equal than the system (MCLK) frequency.

#### 10.2.1 Watchdog timer+ Counter

The watchdog timer+ counter (WDTCNT) is a 16-bit up-counter that is not directly accessible by software. The WDTCNT is controlled and time intervals selected through the watchdog timer+ control register WDTCTL.

The WDTCNT can be sourced from ACLK or SMCLK. The clock source is selected with the WDTSSEL bit.

#### 10.2.2 Watchdog Mode

After a PUC condition, the WDT+ module is configured in the watchdog mode with an initial 32768 cycle reset interval using the DCOCLK. The user must setup, halt, or clear the WDT+ prior to the expiration of the initial reset interval or another PUC will be generated. When the WDT+ is configured to operate in watchdog mode, either writing to WDTCTL with an incorrect password, or expiration of the selected time interval triggers a PUC. A PUC resets the WDT+ to its default condition and configures the RST/NMI pin to reset mode.

#### 10.2.3 Interval Timer Mode

Setting the WDTTMSEL bit to 1 selects the interval timer mode. This mode can be used to provide periodic interrupts. In interval timer mode, the WDTIFG flag is set at the expiration of the selected time interval. A PUC is not generated in interval timer mode at expiration of the selected timer interval and the WDTIFG enable bit WDTIE remains unchanged.

When the WDTIE bit and the GIE bit are set, the WDTIFG flag requests an interrupt. The WDTIFG interrupt flag is automatically reset when its interrupt request is serviced, or may be reset by software. The interrupt vector address in interval timer mode is different from that in watchdog mode.

#### Note: Modifying the Watchdog timer+

The WDT+ interval should be changed together with WDTCNTCL = 1 in a single instruction to avoid an unexpected immediate PUC or interrupt.

The WDT+ should be halted before changing the clock source to avoid a possible incorrect interval.

#### 10.2.4 Watchdog Timer+ Interrupts

The WDT+ uses two bits in the SFRs for interrupt control.

The WDT+ interrupt flag, WDTIFG, located in IFG1.0

The WDT+ interrupt enable, WDTIE, located in IE1.0

When using the WDT+ in the watchdog mode, the WDTIFG flag sources a reset vector interrupt. The WDTIFG can be used by the reset interrupt service routine to determine if the watchdog caused the device to reset. If the flag is set, then the watchdog timer+ initiated the reset condition either by timing out or by a security key violation. If WDTIFG is cleared, the reset was caused by a different source.

When using the WDT+ in interval timer mode, the WDTIFG flag is set after the selected time interval and requests a WDT+ interval timer interrupt if the WDTIE and the GIE bits are set. The interval timer interrupt vector is different from the reset vector used in watchdog mode. In interval timer mode, the WDTIFG flag is reset automatically when the interrupt is serviced, or can be reset with software.

#### 10.2.5 Watchdog Timer+ Clock Fail-Safe Operation

The WDT+ module provides a fail-safe clocking feature assuring the clock to the WDT+ cannot be disabled while in watchdog mode. This means the low-power modes may be affected by the choice for the WDT+ clock. For example, if ACLK is the WDT+ clock source, LPM4 will not be available, because the WDT+ will prevent ACLK from being disabled. Also, if ACLK or SMCLK fail while sourcing the WDT+, the WDT+ clock source is automatically switched to MCLK. In this case, if MCLK is sourced from a crystal, and the crystal has failed, the fail-safe feature will activate the DCO and use it as the source for MCLK.

When the WDT+ module is used in interval timer mode, there is no fail-safe feature for the clock source.

## 10.2.6 Operation in Low-Power Modes

The MSP430 devices have several low-power modes. Different clock signals are available in different low-power modes. The requirements of the user's application and the type of clocking used determine how the WDT+ should be configured. For example, the WDT+ should not be configured in watchdog mode with SMCLK as its clock source if the user wants to use low-power mode 3 because the WDT+ will keep SMCLK enabled for its clock source, increasing the current consumption of LPM3. When the watchdog timer+ is not required, the WDTHOLD bit can be used to hold the WDTCNT, reducing power consumption.

#### 10.2.7 Software Examples

Any write operation to WDTCTL must be a word operation with 05Ah (WDTPW) in the upper byte:

## 10.3 Watchdog Timer+ Registers

The WDT+ registers are listed in Table 10-1.

Table 10-1. Watchdog timer+ Registers

| Register                         | Short Form | Register Type | Address | Initial State               |

|----------------------------------|------------|---------------|---------|-----------------------------|

| Watchdog timer+ control register | WDTCTL     | Read/write    | 0120h   | 06900h with PUC             |

| SFR interrupt enable register 1  | IE1        | Read/write    | 0000h   | Reset with PUC              |

| SFR interrupt flag register 1    | IFG1       | Read/write    | 0002h   | Reset with PUC <sup>†</sup> |

<sup>&</sup>lt;sup>†</sup> WDTIFG is reset with POR

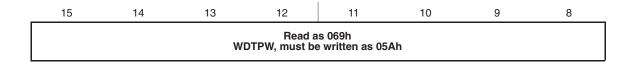

## WDTCTL, Watchdog Timer+ Register

| 7       | 6        | 5      | 4        | 3        | 2       | 1               | 0    |

|---------|----------|--------|----------|----------|---------|-----------------|------|

| WDTHOLD | WDTNMIES | WDTNMI | WDTTMSEL | WDTCNTCL | WDTSSEL | WD <sup>-</sup> | ГІЅх |

| rw-0    | rw-0     | rw-0   | rw-0     | r0(w)    | rw-0    | rw-0            | rw-0 |

**WDTPW** Bits Watchdog timer+ password. Always read as 069h. Must be written as 05Ah, 15-8 or a PUC will be generated.

**WDTHOLD** Bit 7 Watchdog timer+ hold. This bit stops the watchdog timer+. Setting WDTHOLD = 1 when the WDT+ is not in use conserves power.

> Watchdog timer+ is not stopped 0

Watchdog timer+ is stopped 1

WDTNMIES Bit 6 Watchdog timer+ NMI edge select. This bit selects the interrupt edge for the NMI interrupt when WDTNMI = 1. Modifying this bit can trigger an NMI. Modify this bit when WDTIE = 0 to avoid triggering an accidental NMI.

> NMI on rising edge 0 1 NMI on falling edge

**WDTNMI** Bit 5 Watchdog timer+ NMI select. This bit selects the function for the RST/NMI pin.

> 0 Reset function

1 NMI function

WDTTMSEL Bit 4 Watchdog timer+ mode select

Watchdog mode

1 Interval timer mode

WDTCNTCL Bit 3 Watchdog timer+ counter clear. Setting WDTCNTCL = 1 clears the count

value to 0000h. WDTCNTCL is automatically reset.

0 No action

WDTCNT = 0000h 1

**WDTSSEL** Bit 2 Watchdog timer+ clock source select

> 0 SMCLK

1 ACLK

**WDTISx** Bits Watchdog timer+ interval select. These bits select the watchdog timer+ 1-0

interval to set the WDTIFG flag and/or generate a PUC.

Watchdog clock source /32768

01 Watchdog clock source /8192

10 Watchdog clock source /512

Watchdog clock source /64 11

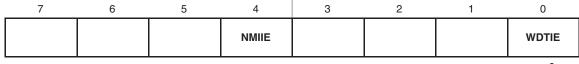

## IE1, Interrupt Enable Register 1

rw-0

Bits These bits may be used by other modules. See device-specific data sheet. 7-5

NMIIE Bit 4

NMI interrupt enable. This bit enables the NMI interrupt. Because other bits in IE1 may be used for other modules, it is recommended to set or clear this bit using  ${\tt BIS.B}$  or  ${\tt BIC.B}$  instructions, rather than  ${\tt MOV.B}$  or  ${\tt CLR.B}$  instructions.

- 0 Interrupt not enabled

- Interrupt enabled

Bits These bits may be used by other modules. See device-specific data sheet. 3-1

WDTIE Bit 0

Watchdog timer+ interrupt enable. This bit enables the WDTIFG interrupt for interval timer mode. It is not necessary to set this bit for watchdog mode. Because other bits in IE1 may be used for other modules, it is recommended to set or clear this bit using  ${\tt BIS.B}$  or  ${\tt BIC.B}$  instructions, rather than  ${\tt MOV.B}$  or  ${\tt CLR.B}$  instructions.

- 0 Interrupt not enabled

- 1 Interrupt enabled

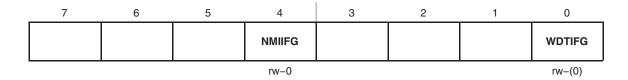

## IFG1, Interrupt Flag Register 1

Bits These bits may be used by other modules. See device-specific data sheet.

7-5

NMIIFG Bit 4 NMI interrupt flag. NMIIFG must be reset by software. Because other bits in IFG1 may be used for other modules, it is recommended to clear NMIIFG by using BIS.B or BIC.B instructions, rather than MOV.B or CLR.B instructions.

0 No interrupt pending

1 Interrupt pending

Bits These bits may be used by other modules. See device-specific data sheet. 3-1

WDTIFG Bit 0 Watchdog timer+ interrupt flag. In watchdog mode, WDTIFG remains set until

reset by software. In interval mode, WDTIFG is reset automatically by servicing the interrupt, or can be reset by software. Because other bits in IFG1 may be used for other modules, it is recommended to clear WDTIFG by using

BIS.B or BIC.B instructions, rather than MOV.B or CLR.B instructions.

0 No interrupt pending

1 Interrupt pending